#### University of Rhode Island

## DigitalCommons@URI

**Open Access Dissertations**

1994

# Data Partition and Migration for High Performance Computation in Distributed Memory Multiprocessors

Nagesh Anupindi University of Rhode Island

Follow this and additional works at: https://digitalcommons.uri.edu/oa\_diss

Terms of Use

All rights reserved under copyright.

#### **Recommended Citation**

Anupindi, Nagesh, "Data Partition and Migration for High Performance Computation in Distributed Memory Multiprocessors" (1994). *Open Access Dissertations*. Paper 779. https://digitalcommons.uri.edu/oa\_diss/779

This Dissertation is brought to you by the University of Rhode Island. It has been accepted for inclusion in Open Access Dissertations by an authorized administrator of DigitalCommons@URI. For more information, please contact digitalcommons-group@uri.edu. For permission to reuse copyrighted content, contact the author directly.

# DATA PARTITION AND MIGRATION FOR HIGH PERFORMANCE COMPUTATION IN DISTRIBUTED MEMORY MULTIPROCESSORS

#### BY NAGESH ANUPINDI

# A DISSERTATION SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN

ELECTRICAL AND COMPUTER ENGINEERING MAJOR PROFESSOR: QING YANG

THE UNIVERSITY OF RHODE ISLAND 1994

# DOCTOR OF PHILOSOPHY DISSERTATION OF NAGESH ANUPINDI

APPROVED:

Dissertation Committee

Major Professor

Professor Ving Yang

Professor Ramdas Kumaresan

Professor Edmund Lamagna

Professor Ravikumar Bala

DEAN OF THE GRADUATE SCHOOL

THE UNIVERSITY OF RHODE ISLAND

1994

TO

MASTERS EK AND CVV,

AMMA, NAANNA, AND SUNDAR

### Abstract

Data-partition and migration for efficient communication in distributed memory architectures are critical for performance of data parallel algorithms. This research presents a formal methodology for the process of data-distribution and redistribution using tensor products and stride permutations as mathematical tools. The algebraic expressions representing data-partition and migration directly operate on a data vector, and hence can be conveniently embedded into an algorithm. It is also shown that these expressions are useful for a clear understanding and to efficiently interleave problems that involve different data-distributions at different phases. This compatibility made us successfully utilize these expressions in developing and demonstrating matrix transpose and fast Fourier transform algorithms. Usage of these expressions for data interface generated efficient parallel implementation to solve Euler partial differential equation. An endeavor to minimize communication cost using expressions for data-distribution disclosed a routing scheme for Fourier transform evaluation. Results promised that for large parallel machines, this scheme is a solution to today's problems which feature enormous data. Finally, a unique data-distribution technique that effectively uses transpose algorithms for multiplication of two rectangular matrices is derived. Performance of these algorithms are evaluated by carrying out implementations on Intel's i860 based iPSC/860, Touchstone Delta, Gamma, and Paragon supercomputers.

# Acknowledgments

This is most pleasant part of writing for I get a chance to thank all those who helped make this dissertation an enjoyable one. I thank Professor James W. Cooley for inspiring the idea of Fourier transform algorithms with respect to parallel machines, for several helpful suggestions, and for recommending me for departmental financial assistance. I also thank Professor Qing Yang for providing financial support through NSF grant MIP-9208041, and for his valuable discussions and suggestions. He also introduced me to the area of high performance computing, and helped me to present this work in an elegant form. Special thanks to Professor Richard Tolimieri and Professor Myoung An for their valuable discussions, moral support, friendship, and financial support through Aware Inc., Cambridge, MA. I am also thankful to Prof. John Weiss at Aware Inc., for introducing and guiding me through the partial differential equation solvers.

I am grateful to the faculty/staff members and fellow students in the Department of Electrical Engineering, who never hesitated to offer timely assistance and warm friendship. I am also grateful to all members of my thesis committee, Professor Ramdas Kumaresan, Professor Edmund Lamagna, and Professor Jein-Chung Lo for their precious time and efforts. I would like to thank Professor Ravikumar Bala for being the chairman of the committee. I thank University of Rhode Island, and Intel Inc., for making their computer power available to carry out the necessary experiments in this dissertation without which this work is not feasible. Special thanks to Dr. Dane P. Kottke for his assistance.

I am indebted to my parents Mr. Kameswara Rao Anupindi and Mrs. Kameswari Anupindi for devoting their souls to give me this beautiful life, and my brother Mr. Sundar Ram Anupindi for memories of a life time.

Nagesh Anupindi

### **Preface**

The demand for high speed computers has been more than existing computing power at any time in the computer era. Even very impressive electronic components could not satisfy today's thirst for performing enormous number of calculations involved in most of the practical applications. With these challenges, parallel processing is the way to achieve desired computing speeds. A parallel computer consists of a collection of processing units that assist together to solve an application. Architects of parallel computers have the freedom to select number of processing units, to link processors through various interconnections, to have shared or distributed memory, to design synchronous or asynchronous operations, etcetera.

For academic researchers, access to supercomputers is still limited. Nonetheless, usage of supercomputers by the community of scientists is increasing every year, and research projects performed on these became more ambitious and sophisticated. To solve problems once thought impractical, supercomputers have become friendly tools.

This dissertation addresses aspects in parallel systems which have distributed memory and feature independence from underlying interconnection network. The problems studied in this dissertation are based on mathematical tools which can represent algorithms for parallel systems. Examples are used as often as possible to illustrate these tools. Distributing the problem onto processors is modeled using these tools while they were proven to be helpful to optimize old solutions as well as to derive new solutions. A list of references to publications where related problems and algorithms are treated is provided at the end.

Nagesh Anupindi

# Contents

| A  | bstra                          | $\mathbf{ct}$                            | ii   |  |  |

|----|--------------------------------|------------------------------------------|------|--|--|

| A  | cknov                          | wledgments                               | iii  |  |  |

| P  | reface                         |                                          | iv   |  |  |

| Ta | able o                         | of Contents                              | v    |  |  |

| Li | st of                          | Tables                                   | viii |  |  |

| Li | st of                          | Figures                                  | ix   |  |  |

| 1  | Intr                           | oduction                                 | 1    |  |  |

| 2  | Preliminaries and Related Work |                                          |      |  |  |

|    | 2.1                            | Introduction                             | 7    |  |  |

|    | 2.2                            | Operators Mat and Vect                   | 8    |  |  |

|    | 2.3                            | Stride Permutation                       | 8    |  |  |

|    | 2.4                            | Tensor Product                           | 9    |  |  |

|    | 2.5                            | Some Useful Theorems                     | 13   |  |  |

|    | 2.6                            | Existing Data-Partition Representations  | 15   |  |  |

|    | 2.7                            | Existing Multidimensional FFT Algorithms | 16   |  |  |

|    | 2.8                            | Survey of Matrix Algorithms              | 18   |  |  |

|    | 2.9                            | Experimental Environment                 | 19   |  |  |

|    | 2.10                           | Conclusion                               | 21   |  |  |

| 3 | Dat | ta Partition and Migration: Formal Definitions                    | 22 |

|---|-----|-------------------------------------------------------------------|----|

|   | 3.1 | Storing Data in Distributed Memories                              | 22 |

|   | 3.2 | Moving Data Among Distributed Memories                            | 26 |

|   |     | 3.2.1 Performance Evaluation of Three Transpose Algorithms        | 31 |

|   | 3.3 | An Example                                                        | 33 |

|   | 3.4 | Comparison of Our Definitions with Related Work                   | 36 |

|   | 3.5 | Conclusion                                                        | 38 |

| 4 | Swi | tching Data Partition Schemes Within An Application               | 39 |

|   | 4.1 | Introduction                                                      | 39 |

|   | 4.2 | Brief Description of Application                                  | 40 |

|   | 4.3 | Switching Between Data-Partitions                                 | 42 |

|   |     | 4.3.1 2D-FFT from Mesh-Division via Column-Division: Algorithm-1  | 42 |

|   |     | 4.3.2 2D-FFT from Mesh-Division via Column-Division: Algorithm-2  | 45 |

|   | 4.4 | Effect of Varying Data Structures on Overall Performance: Results |    |

|   |     | and Conclusion                                                    | 47 |

| 5 | AN  | New Approach for FFT Algorithm with Mesh-Division                 | 51 |

|   | 5.1 | Introduction                                                      | 51 |

|   | 5.2 | New Approach                                                      | 53 |

|   |     | 5.2.1 Proof                                                       | 58 |

|   | 5.3 | Performance Evaluation and Comparison                             | 60 |

|   | 5.4 | Conclusion                                                        | 61 |

| 6 | Par | allel Matrix Multiplication Algorithm For Rectangular Arrays      | 63 |

|   | 6.1 | Introduction                                                      | 63 |

|   | 6.2 | Broadcast-and-Shift Matrix Multiplication Algorithm               | 64 |

|   | 6.3 | Two Extremes of Broadcast-and-Shift Algorithm                     | 66 |

|   | 6.4 | New Approach: Taking Advantage of Two Extremes                    | 68 |

|   | 6.5 | Performance Evaluation                                            | 71 |

|   | 6.6 | Conclusion                                                        | 73 |

| 7 Conclusions and Future Research          | 76 |

|--------------------------------------------|----|

| A Tensor Product Representation of 3D-FFT  | 78 |

| B Three Dimensional FFT using New Approach | 81 |

| List of References                         | 82 |

| Bibliography                               | 90 |

,

# List of Tables

| 1.1  | Results of experiments to determine the start-up and transmission times | 5  |

|------|-------------------------------------------------------------------------|----|

| 3.2  | Pseudo-code for message passing in transpose algorithms for either      |    |

|      | row-division or column-division partitions                              | 28 |

| 3.3  | Experimental results of transpose algorithms on Intel's Paragon         | 31 |

| 3.4  | Experimental results of transpose algorithms on Intel's Touchstone      |    |

|      | Delta                                                                   | 32 |

| 4.5  | Two-dimensional double-precision complex FFT implementation re-         |    |

|      | sults for (1) $iPSC/860$ library code, (2) Interface routines appended  |    |

|      | at input and output, (3) Algorithm-1, and (4) Algorithm-2               | 46 |

| 4.6  | Timing results for $128 \times 128$ size vorticity computations         | 50 |

| 5.7  | Implementation results of FFT using new approach on Intel's Touch-      |    |

|      | stone Delta                                                             | 62 |

| 6.8  | Timing results for routing scheme in new matrix multiplication algo-    |    |

|      | rithm for 2, 4, 8 and 16-node partitions                                | 71 |

| 6.9  | Timing results for routing schemes in matrix multiplication algorithms  |    |

|      | on Intel's Paragon with 16-processors                                   | 72 |

| 6.10 | Timing results for routing schemes in matrix multiplication algorithms  |    |

|      | on Touchstone Delta with 16-processors                                  | 74 |

| 6.11 | Timing results for routing schemes in matrix multiplication algorithms  |    |

|      | on $iPSC/860$ with 16-processors                                        | 75 |

# List of Figures

| 3.1 | Action of data-partition algebraic expressions onto a 4-processor ma-    |    |

|-----|--------------------------------------------------------------------------|----|

|     | chine                                                                    | 25 |

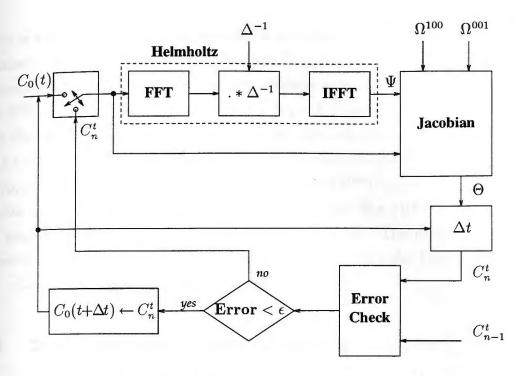

| 4.2 | Flow Chart for computation of coefficients of Vorticity                  | 41 |

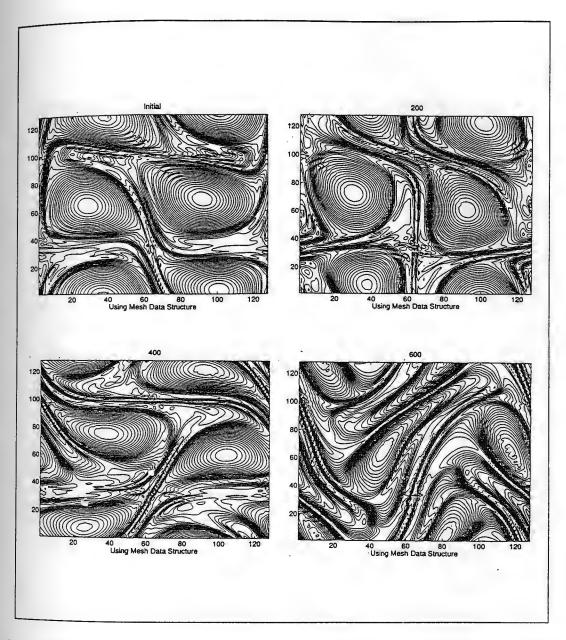

| 4.3 | Contour plots of the Initial vorticity function and for time steps 200,  |    |

|     | 400, and 600                                                             | 48 |

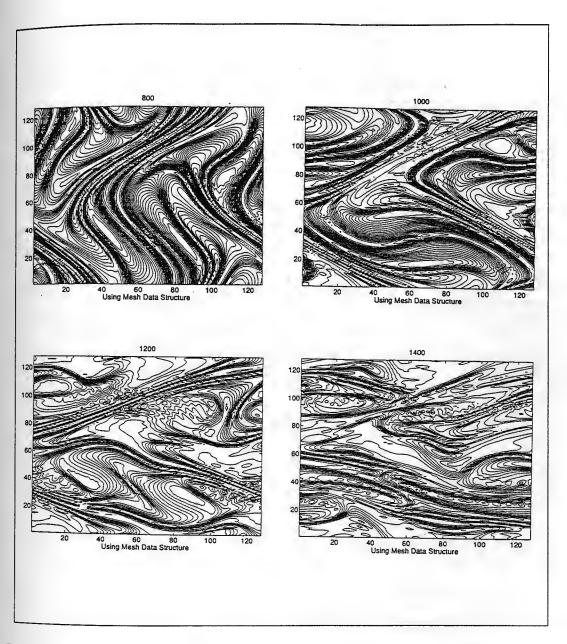

| 4.4 | Contour plots of the vorticity functions for time steps 800, 1000, 1200, |    |

|     | and 1400                                                                 | 49 |

| 5.5 | Mapping of 2-D array $f(x,y)$ onto 6-D array                             | 54 |

| 6.6 | Broadcast-and-Shift Matrix Multiplication Algorithm on 16-processors     | 64 |

| 6.7 | Broadcast-and-Shift Multiplication using 4-processor machine (a) for     |    |

|     | row-division with no broadcasts in A and (b) for column-division with    |    |

|     | no shifts in <b>B</b>                                                    | 67 |

| 6.8 | New Approach for Matrix Multiplication Algorithm on 4-processors .       | 68 |

| A.1 | Data-partitioning for Intel's 3D-FFT algorithm                           | 78 |

# Chapter 1

## Introduction

Many scientific computations such as engineering, energy resource, medical, military, artificial intelligence, and basic research areas demand fast processing computers to achieve required computational performance. Without the existence of superpower computers, the study of many of these applications and the efforts to meet today's challenges could hardly be realized. Since device characteristics are approaching the physical limit, parallel processing is the only way to improve computing power further in order to meet its ever increasing demand. Research in cost-effective, high-speed, massively parallel, and reliable supercomputers has become a very active field in computer engineering.

Two distinct and important parallel computer architectures are shared-memory, and message-passing systems [1, 2]. A shared-memory machine has a single global memory accessible to all processors such as IBM RP3, Encore Multimax, Cray X-MP, and many workstations. Its important feature is that communication between nodes is done by reading from and writing into the shared-memory. However, the shared-memory builds a barrier for increasing number of processing elements. Message-passing systems, also known as distributed memory system, allocate a stipulated amount of memory to each processing element but data does not form a single address space [3]. Communication among processors is done through message-passing. Intel iPSC, nCube, and Caltech Mark II hypercube belong to this category. In this

architecture, if an application shares data at distinct nodes, a programmer specifically commands to port data from one node to another. Since no resources such as data, cache, CPU time, etc., are globally shared besides the links (a link is accessible to a very limited number of processors), message-passing systems are scalable and preferred by researchers for solving larger problems.

One important characteristic of message-passing machines (also known as distributed memory systems) is that there is a significant timing difference between local and remote data accesses. Remote data access involves message-passing among processors. This message-passing process takes a significant amount of total execution time of a computational procedure. The amount of remote data accesses needed to accomplish a given computation mainly depends upon how data are initially allocated to processors. We refer to this initial data allocation as data-partition. Efficient data-partition in distributed memory systems is essential for achieving high performance of data parallel programs. An optimal data-partition for one individual algorithm (computation module) may not be optimal for others. Therefore, optimized data-partition for applications that involve a number of computation algorithms or modules present an interesting challenge to parallel processing researchers.

Optimization of data-partition is achieved mainly by constraining to a rule that number of message-passings should be minimum for a given system architecture. The system architecture of a distributed memory system is mainly determined by its interconnection structure. Various interconnection networks and evaluation of their performance have been reported in the literature [4, 5, 6, 7]. Some well known network schemes for message-passing systems are ring, tree, mesh, hypercube and star connections. Processors that are directly connected are called neighbors. Processors that are not connected through a direct link are called non-neighbors. Distance between processors is calculated based on the minimum number of processors through which they are connected. It was also observed that the farther the node is, the longer it takes to port data. Hence, the performance of an implementation can be optimized by minimizing the distance a node has to travel to get data. Extensive

efforts have been put forth in minimizing communication distance among processors in a research field called *parallel programming* [8, 9].

Recently, a very important technological advancement has occurred in interconnection networks to minimize communication cost known as wormhole routing [10, 11]. In this scheme, a message is divided into a number of flits (flow control digits). Once the header flit of a message acquires a channel, it governs the route of that message and the remaining flits follow in a pipelined fashion. This pipelined nature of wormhole routing procedures resulted in a network latency that is relatively insensitive to the distance between processors [12], which in turn has made communication cost to predominantly depend upon message lengths and the number of messages. These features have attracted commercial multicomputers such as the Intel's Touchstone Delta and Intel's Paragon which use wormhole routing in a 2D mesh, and MIT's J-machine which uses wormhole routing in 3D mesh. Ametek 2010 used a mesh network renamed as Symult 2010 after adopting wormhole routing. The nCube-2 which originally used hypercube topology has now adopted wormhole routing.

With wormhole routing, passing a message from one node to another requires a specific start-up (overhead) time,  $t_{start}$ , and a transmission time that depends upon the length of the message. Let  $t_{element}$  be the time for an 8-byte data to pass through an acquired channel. Then a simple model for total communication time for a message of l-bytes is given by

$$t_{total} = t_{start} + (l/8) t_{element}. (1.1)$$

We conducted experiments to determine the relationship between start-up time and transmission time on several machines. Table 1.1 shows the results of our experiments to obtain start-up time and time to communicate 8-bytes (one complex number) of data on Intel's Paragon, Gamma, and Touchstone Delta. Results are obtained by averaging observed timings over 100 samples for passing a message from each node to every other node. Possible machine-partitions (machine-partition is a cluster of nodes that is subset of all the nodes on a machine. For example, a cluster of 16

nodes on 512-node Touchstone Delta is a 16-node machine-partition) are considered for each machine to observe the effect of node's distance on total communication time. It is observed that the ratio between start-up time and transmission time remains almost constant irrespective of physical distance between nodes, implying performance results close to a fully connected distributed system. Understanding such features of new machines with respect to their latency of message-passing helps parallel programmers to develop efficient algorithms.

Because of the importance of data-partition in data parallel programs, we focused our attention on the study of partitioning an application and migrating the necessary data among processors. This dissertation formulates the data-partitioning schemes and derives variants of migrating schemes in distributed memory multiprocessor systems using tensor algebra. The essential feature of this formulation is that data-partition and migration are represented using simple tensor algebraic expressions. Therefore, they can form parts of an algorithm that is already written in tensor algebraic notation. Furthermore, by using tensor notation and stride permutations, our formulation is simple and compact without having to deal with complicated indices in complex data structures. Such a clear mathematical representation of storage schemes helps parallel programmers greatly to look into inherent structure(s) of an algorithm and the associated communication cost.

With the newly proposed formulations, optimal data-migration at interfaces between computation modules become straightforward algebraic manipulations. This research demonstrates the manipulations of fast Fourier transform (FFT) algorithms for efficient implementations. These algorithms are applied to an application that solves Euler partial differential equation using wavelet-Galerkin method and achieved a significant improvement in the overall performance. Then, we have designed an efficient two-dimensional FFT algorithm for distributed systems using algebraic expressions for mesh-division data-partitioning. This design is shown to be a solution to the problems featuring huge data size, large machines and higher dimensionality. Optimal data-partition is considered also for matrix multiplication algorithms

| Number of | of Paragon  |                      | Gamma       |               | Delta       |                  |

|-----------|-------------|----------------------|-------------|---------------|-------------|------------------|

| Nodes     | $t_{start}$ | $t_{element}$        | $t_{start}$ | $t_{element}$ | $t_{start}$ | $t_{element}$    |

|           | (msec)      | $(\mu \mathrm{sec})$ | (msec)      | $\mu sec$     | (msec)      | $(\mu { m sec})$ |

| 4         | 4.330       | 0.922                | 2.753       | 5.734         | 1.046       | 2.560            |

| 8         | 4.411       | 0.939                | 2.981       | 6.357         | 1.355       | 3.328            |

| 16        | 4.445       | 0.934                |             |               | 1.548       | 3.757            |

| 32        | 4.503       | 0.985                |             |               | 1.777       | 4.541            |

| 64        | 4.512       | 0.989                |             |               | 1.831       | 4.521            |

| 128       |             |                      |             |               | 1.910       | 4.658            |

| 256       |             |                      |             |               | 1.921       | 4.708            |

Table 1.1: Results of experiments to determine the start-up and transmission times where we have shown that distributed transpose algorithms can be efficiently used for multiplying two rectangular arrays.

In order to demonstrate the usefulness and significance of our data-partition expressions, we carried out implementations of our algorithms and applications on Intel's supercomputers: iPSC/860, Paragon, Gamma, and Touchstone Delta.

This dissertation is organized as follows: Chapter 2 reviews the tensor algebraic notation, and related theorems that are required for a better understanding of the concepts in our contributions. It also presents a survey of the existing literature that is related to this dissertation. Chapter 3 presents definitions for three data-allocation schemes in tensor algebraic notation. Demonstration of these expressions is presented for the case of matrix transpose algorithms using all the three distinct data-allocation schemes. This chapter also presents tensor product formulation of two-dimensional discrete Fourier transform (2D-DFT) for row-division data-partition using the transpose algorithms. Computation of vorticity and stream functions in two-dimensional fluid turbulence using 2D-DFT is carried out in Chapter 4 to demonstrate the usage of data-allocation expressions to efficiently interface two computation modules

that are efficient for two different data-partition schemes. A new and highly efficient approach to evaluate large 2D-DFTs using large parallel computers is derived using tensor algebra in Chapter 5. Chapter 6 considers the matrix multiplication algorithms for distributed memory systems via matrix transpose algorithm by presenting a unique data allocation scheme for rectangular multiplicands. Chapter 7 discusses future research and possible extensions of the methods developed in this work to other algorithms.

# Chapter 2

# Preliminaries and Related Work

#### 2.1 Introduction

In a distributed environment, implementation procedure for most of the applications involves dividing the main computational task into (a) local tasks that depend upon data residing at a node's local memory, and (b) global tasks that depend upon data residing at more than one node. Such an identification and separation gives an estimation of the degree of node balance in an implementation and also the inherent message-passing overheads. Tensor algebra is a mathematical language that aids to identify, express, and analyze these tasks in an algorithm. Two most important operations in tensor algebra are tensor products, and stride permutations. In the following sections, we introduce these operations and demonstrate their importance with respect to parallel machines. This notation is used in Chapter 3 to develop a set of formal definitions for data-partition schemes. Later parts of Chapter 3 use the same notation to express matrix transpose algorithms, and multidimensional fast Fourier transform (FFT) calculations with an emphasis on their implementation aspects for a distributed memory system. Also, Chapters 4 and 5 deal with variants of FFT algorithms using the same notation.

Sections 2.2 through 2.5 review the necessary notation and relevant theorems to this dissertation from tensor algebra. Survey of the literature related to data-partitioning schemes is presented in Section 2.6 while that for FFT algorithms and matrix computations are presented in Sections 2.7 and 2.8, respectively. Section 2.9 gives a brief description of the machines on which experiments in this dissertation are conducted. Section 2.10 concludes the chapter.

## 2.2 Operators Mat and Vect

Let **x** be KJ-element vector:  $[x_0 \ x_1 \ \dots, \ x_{KJ}]^T$ . The matrix operator,  $Mat_{K\times J}$ , converts **x** into a  $K\times J$  matrix as follows.

$$\mathbf{X} = Mat_{K \times J}(\mathbf{x}) = \begin{bmatrix} x_0 & x_K & \dots & x_{(J-1)K} \\ x_1 & x_{K+1} & \dots & x_{(J-1)K+1} \\ x_2 & x_{K+2} & \dots & x_{(J-1)K+2} \\ \vdots & \vdots & \ddots & \vdots \\ x_{K-1} & x_{2K-1} & \dots & x_{JK-1} \end{bmatrix}$$

(2.2)

The inverse operation of Mat,  $Vect_{KJ}$ , forms a linear array according to column-major scheme as follows.

$$\mathbf{x} = Vect_{KJ}(\mathbf{X}) = Vect_{JK} \begin{pmatrix} x_0 & x_K & \dots & x_{(J-1)K} \\ x_1 & x_{K+1} & \dots & x_{(J-1)K+1} \\ x_2 & x_{K+2} & \dots & x_{(J-1)K+2} \\ \vdots & \vdots & \ddots & \vdots \\ x_{K-1} & x_{2K-1} & \dots & x_{JK-1} \end{pmatrix}$$

(2.3)

### 2.3 Stride Permutation

Stride permutations are natural way of representing data-shuffling operations. We use  $P(L_x, S)$  to represent a stride permutation operation on a vector of length  $L_x$  with stride S. Let  $\mathbf{x}$  be an  $L_sS$ -element vector and  $L_x = L_sS$ . Then, the stride

permutation,  $\mathbf{y} = P(L_x, S)\mathbf{x}$ , performs the following operations. The first  $L_s$  elements of  $\mathbf{y}$  are obtained by picking up elements of  $\mathbf{x}$  starting at  $x_0$  and then each Sth element of  $\mathbf{x}$ : that is,  $\{x_0, x_S, \dots x_{(L_s-1)S}\}$ . The next  $L_s$  elements of  $\mathbf{y}$  are obtained in the same way starting at  $x_1$  of  $\mathbf{x}$ :  $\{x_1, x_{S+1}, \dots, x_{(L_s-1)S+1}\}$ , and so on. Therefore, the stride permutation operation,  $P(L_x, S)$ , is an  $L_x \times L_x$  size matrix that is filled with zeros and ones.

Example 2.1 Permutation matrix P(6,3) shown below is operating on vector  $\mathbf{x} = [x_0 \ x_1 \ x_2 \ x_3 \ x_4 \ x_5]^T$ , and denoted as  $\mathbf{y} = P(6,3)\mathbf{x}$ .

$$\mathbf{y} = \begin{bmatrix} x_0 \\ x_3 \\ x_1 \\ x_4 \\ x_2 \\ x_5 \end{bmatrix} = \underbrace{\begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 \end{bmatrix}}_{P(6,3)} \begin{bmatrix} x_0 \\ x_1 \\ x_2 \\ x_3 \\ x_4 \\ x_5 \end{bmatrix}$$

(2.4)

#### 2.4 Tensor Product

Tensor product is a binary operator between two matrices of any size. Given two matrices **A** and **B** of sizes  $M_A \times N_A$  and  $M_B \times N_B$ , respectively, a new matrix, **C**, dimensioned  $M_A M_B \times N_A N_B$  can be generated by tensor product of **A** and **B** as:

$$\mathbf{C} = \mathbf{A} \otimes \mathbf{B} = \begin{bmatrix} a_{(0,0)}\mathbf{B} & a_{(0,1)}\mathbf{B} & a_{(0,2)}\mathbf{B} & \dots & a_{(0,N_{A}-1)}\mathbf{B} \\ a_{(1,0)}\mathbf{B} & a_{(1,1)}\mathbf{B} & a_{(1,2)}\mathbf{B} & \dots & a_{(1,N_{A}-1)}\mathbf{B} \\ a_{(2,0)}\mathbf{B} & a_{(2,1)}\mathbf{B} & a_{(2,2)}\mathbf{B} & \dots & a_{(2,N_{A}-1)}\mathbf{B} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ a_{(M_{A}-1,0)}\mathbf{B} & a_{(M_{A}-1,1)}\mathbf{B} & a_{(M_{A}-1,2)}\mathbf{B} & \dots & a_{(M_{A}-1,N_{A}-1)}\mathbf{B} \end{bmatrix}$$

(2.5)

where  $a_{(i,j)}$  is the element at *i*th row and *j*th column of **A**, and  $a_{(i,j)}$ **B** is scalar matrix multiplication. In other words, tensor product is a list of all possible combinations of multiplications of one matrix's elements with the other's.

Example 2.2 Consider two matrices A and B as:

$$\mathbf{A} = \begin{bmatrix} 1 & 2 \\ 3 & 4 \end{bmatrix} \quad and \quad \mathbf{B} = \begin{bmatrix} 10 & 11 & 12 \\ 13 & 14 & 15 \end{bmatrix}.$$

Then

$$\mathbf{C} = \mathbf{A} \otimes \mathbf{B} = \begin{bmatrix} \mathbf{B} & 2\mathbf{B} \\ 3\mathbf{B} & 4\mathbf{B} \end{bmatrix} = \begin{bmatrix} 10 & 11 & 12 & 20 & 22 & 24 \\ 13 & 14 & 15 & 26 & 28 & 30 \\ \hline 30 & 33 & 36 & 40 & 44 & 48 \\ 39 & 42 & 45 & 52 & 56 & 60 \end{bmatrix}$$

according to equation (2.5).

Two types of tensor products are of special interest to us here from the point of parallel computations. One has an identity matrix on the left-hand side of the tensor product as  $\mathbf{I} \otimes \mathbf{A}$ , called *prior identity matrix*, and the other has an identity matrix on the right-hand side such as  $\mathbf{A} \times \mathbf{I}$ , referred as *post identity matrix*. For the rest of the discussion in this section, let a vector  $\mathbf{x}$  be of length  $L_x = JN_A$ , vector  $\mathbf{y}$  be of length  $L_y = JM_A$ , matrix  $\mathbf{I}_J$  be identity matrix of size  $J \times J$ , and  $\emptyset_{M_A \times N_A}$  be a null matrix of size  $M_A \times N_A$ .

When tensor product of an identity matrix  $I_J$  with a matrix A of size  $M_A \times N_A$  is applied on a vector  $\mathbf{x}$ , it can be written as

$$\mathbf{y}_{JM_A} = \left[ \mathbf{I}_J \otimes \mathbf{A}_{M_A \times N_A} \right] \mathbf{x}_{JN_A} \tag{2.6}$$

The above equation can be expanded using the definition of tensor product as

$$\begin{bmatrix} y_0 \\ y_1 \\ y_2 \\ \vdots \\ y_{L_y-1} \end{bmatrix} = \begin{bmatrix} \mathbf{A}_{M_A \times N_A} & \emptyset_{M_A \times N_A} & \emptyset_{M_A \times N_A} & \dots & \emptyset_{M_A \times N_A} \\ \emptyset_{M_A \times N_A} & \mathbf{A}_{M_A \times N_A} & \emptyset_{M_A \times N_A} & \dots & \emptyset_{M_A \times N_A} \\ \emptyset_{M_A \times N_A} & \emptyset_{M_A \times N_A} & \mathbf{A}_{M_A \times N_A} & \dots & \emptyset_{M_A \times N_A} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ \emptyset_{M_A \times N_A} & \emptyset_{M_A \times N_A} & \emptyset_{M_A \times N_A} & \dots & \mathbf{A}_{M_A \times N_A} \end{bmatrix} \begin{bmatrix} x_0 \\ x_1 \\ x_2 \\ \vdots \\ x_{L_x-1} \end{bmatrix}, (2.7)$$

which can also be expressed using operators Mat and Vect as

$$\mathbf{y}_{JM_A} = Vect_{M_AJ} \left\{ \mathbf{A}_{M_A \times N_A} \left( Mat_{N_A \times J} (\mathbf{x}_{L_x}) \right) \right\}$$

(2.8)

On a J-processor architecture, this representation gives a mechanism of simultaneously operating matrix A on different parts of input data by different processors.

Example 2.3 Consider a 4-processor machine and the following operational matrix A to be operated on vector x:

$$\mathbf{A} = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix} \quad and \quad \mathbf{x} = \begin{bmatrix} x_0 \ x_1 \ x_2 \ x_3 \ x_4 \ x_5 \ x_6 \ x_7 \end{bmatrix}^T.$$

Then,  $y = (I_4 \otimes A) x =$

$$\begin{bmatrix} x_0 + x_1 \\ x_0 - x_1 \\ \hline x_2 + x_3 \\ \hline x_2 - x_3 \\ \hline x_4 + x_5 \\ \hline x_6 + x_7 \\ \hline x_6 - x_7 \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & -1 & 0 & 0 & 0 & 0 & 0 & 0 \\ \hline 0 & 0 & 1 & 1 & 0 & 0 & 0 & 0 \\ \hline 0 & 0 & 1 & -1 & 0 & 0 & 0 & 0 \\ \hline 0 & 0 & 0 & 0 & 1 & 1 & 0 & 0 \\ \hline 0 & 0 & 0 & 0 & 0 & 1 & 1 \\ \hline 0 & 0 & 0 & 0 & 0 & 0 & 1 & 1 \\ \hline 0 & 0 & 0 & 0 & 0 & 0 & 1 & -1 \end{bmatrix} \begin{bmatrix} x_0 \\ x_1 \\ x_2 \\ x_3 \\ \hline x_4 \\ x_5 \\ \hline x_6 \\ x_7 \end{bmatrix}$$

Here, each processor executes one addition and one subtraction on a different part of  $\mathbf{x}$ , where the node boundaries are represented by horizontal lines. Execution of the same task on 2-processor machine can be written as  $[\mathbf{I}_2 \otimes (\mathbf{I}_2 \otimes \mathbf{A})]$  representing double amount of computation by each processor.

Therefore, these tensor products with prior identity matrices can be used to determine the existence of local (parallel) tasks. In general, on a k-processor distributed memory machine, execution of  $(\mathbf{I}_J \otimes \mathbf{A})$  would imply k local tasks, where J = nk and n is a positive integer greater than zero.

If an identity matrix appears on the right-hand side of a tensor product, it is performed in a natural way for vector computers, that is, performing an operation

## 2.5 Some Useful Theorems

A number of properties that tensor products hold in combination with stride permutations will be useful in developing variants of a parallel algorithm. We will present these properties here without proof. Interested readers can find their proofs in [13, 14]. Similar to the notation in algebra of matrices, a complex tensor product formulation should be read from right to left.

Theorem 2.1 Associative Law: Tensor product on a set of matrices is associative.

$$(\mathbf{A}_{M_A \times N_A} \otimes \mathbf{B}_{M_B \times N_B}) \otimes \mathbf{C}_{M_C \times N_C} = \mathbf{A}_{M_A \times N_A} \otimes (\mathbf{B}_{M_B \times N_B} \otimes \mathbf{C}_{M_C \times N_C})$$

(2.12)

Theorem 2.2 Distributive Laws: When two matrices A and B are of the same size, following additive distribution law holds true irrespective of the size of matrix C.

$$(\mathbf{A}_{M\times N} + \mathbf{B}_{M\times N}) \otimes \mathbf{C}_{M_C\times N_C}$$

$$= (\mathbf{A}_{M\times N} \otimes \mathbf{C}_{M_C\times N_C}) + (\mathbf{B}_{M\times N} \otimes \mathbf{C}_{M_C\times N_C})$$

(2.13)

Similarly, when two matrices  $\mathbf{B}$  and  $\mathbf{C}$  are of the same size, following additive distribution law holds true irrespective of the size of matrix  $\mathbf{A}$ .

$$\mathbf{A}_{M_A \times N_A} \otimes (\mathbf{B}_{M \times N} + \mathbf{C}_{M \times N})$$

$$= (\mathbf{A}_{M_A \times N_A} \otimes \mathbf{B}_{M \times N}) + (\mathbf{A}_{M_A \times N_A} \otimes \mathbf{C}_{M \times N})$$

(2.14)

Theorem 2.3 Multiplication of Tensor Products: If  $N_X = M_A$  and  $N_Y = M_B$ , then the following multiplication theorem holds true.

$$(\mathbf{X}_{M_X \times N_X} \otimes \mathbf{Y}_{M_Y \times N_Y}) \quad (\mathbf{A}_{M_A \times N_A} \otimes \mathbf{B}_{M_B \times N_B})$$

$$= (\mathbf{X}_{M_X \times N_X} \mathbf{A}_{M_A \times N_A}) \otimes (\mathbf{Y}_{M_Y \times N_Y} \mathbf{B}_{M_B \times N_B})$$

(2.15)

This theorem is quite often used to derive parallel or vector computations when identity matrices appear in the product.

Theorem 2.4 Commutative Law: Interchanging the order of tensor product parameters results in permutations.

$$(\mathbf{A}_{M_A \times N_A} \otimes \mathbf{B}_{M_B \times N_B}) = P(M_A M_B, M_A) (\mathbf{B}_{M_B \times N_B} \otimes \mathbf{A}_{M_A \times N_A}) P(N_A N_B, N_B)$$

(2.16)

This theorem is quite useful in generating different communication structures of an algorithm.

Theorem 2.5 Inverse of Tensor Products: Unlike the case in inverse of multiplication of two matrices, inverse of tensor product of two matrices does not change the order of its parameters.

$$(\mathbf{A} \otimes \mathbf{B})^{-1} = (\mathbf{A}^{-1} \otimes \mathbf{B}^{-1}) \tag{2.17}$$

Theorem 2.6 Multiplication Theorem of Stride Permutations: Any simplestride permutation can be decomposed into two stride permutations when stride is a multiple of two integers.

$$P(N_A N_B N_C, N_A N_B) = P(N_A N_B N_C, N_A) P(N_A N_B N_C, N_B)$$

(2.18)

#### Theorem 2.7 Parallel-Vector Tensor Factorization of Stride Permutations:

$$P(N_A N_B N_C, N_C) = [P(N_A N_C, N_C) \otimes \mathbf{I}_{N_B}] [\mathbf{I}_{N_A} \otimes P(N_B N_C, N_C)]$$

(2.19)

This is one of the very important theorems for implementation of a permutation on distributed memory systems to uncover extent of communication complexity hidden in that permutation. When parameter  $N_A$  is an integral multiple of number of processing elements, this theorem extracts local operations from operations that depend upon non-local data. A stride permutation can also be factorized in a different way leading to the following theorem:

#### Theorem 2.8 Vector-Parallel Tensor Factorization of Stride Permutations:

$$P(N_A N_B N_C, N_A N_B) = [\mathbf{I}_{N_A} \otimes P(N_B N_C, N_B)] [P(N_A N_C, N_A) \otimes \mathbf{I}_{N_B}]$$

(2.20)

Theorem 2.9 Inverse Stride Permutation:

$$P(N_A N_B, N_A)^{-1} = P(N_A N_B, N_B). (2.21)$$

Theorem 2.10 Identity Stride Permutations:

$$P(N_A, N_A) = P(N_A, 1) = \mathbf{I}_{N_A}$$

(2.22)

### 2.6 Existing Data-Partition Representations

It is well known that data-distribution in distributed memory multiprocessors is essential to achieve high performance of data-parallel programs. Extensive research has been reported on data-decomposition optimization for distributed memory machines [15, 16, 17, 18, 19]. Research in this area can be crudely classified into two categories. One aims at finding optimal data-partitioning schemes for parallel loop constructs as part of compiler. It has been shown that the problem of finding an optimal data-partition is NP-complete [17, 20, 15]. Therefore, researchers have to rely on heuristic methods [20, 21, 22, 16, 23]. The other effort aims at special-purpose implementations and a large work force for developing optimal implementation of individual algorithms is reported [24, 25, 26].

Typically, an application requires a number of computation modules linked together to accomplish a specific computation. Global optimization depends not only on optimal implementation of the computational modules, but at least equally on the interface between these implementations as determined by the data partition and migration across processors.

In this dissertation, we present a systematic formulation for data-partition and migration on distributed memory multiprocessors in terms of tensor product notation and stride permutations [27]. Data-partition and migration are represented using simple tensor algebraic expressions highlighting the computational and communication complexity of parallel algorithms. Therefore, optimal data-partition and

migration at interfaces between different algorithms becomes straightforward tensor algebraic manipulations with the aid of well-established theorems in this field. Furthermore, due to the conciseness of the underlying algebra, definitions are simple and compact without having to deal with complicated indices in complex data structures.

In order to demonstrate the significance and usefulness of our framework, we have carried out experiments on existing distributed memory multiprocessors such as Intel's Paragon, and Touchstone Delta. Initially, our formal definitions are incorporated in three application problems: matrix transpose algorithm, two dimensional discrete Fourier transform algorithm, and solution of Euler partial differential equation using wavelet-Galerkin approach. Then, simple algebraic manipulations on these expressions are carried out to derive optimal data-partition and migration schemes. Experimental timing results on these machines show that such simple algebraic manipulations result in performance improvement ranging from 30% to 600%.

# 2.7 Existing Multidimensional FFT Algorithms

The Fourier transform of large multidimensional data sets is an essential computation in many scientific and engineering fields, including seismology, meteorology, x-ray crystallography, radar, sonar and medical imaging. Such fields require multidimensional arrays and large data set for complete and faithful modeling. The development of powerful parallel computers has given scientists a means of studying problems with greater complexity and higher dimensionality. Classically, a set of data is processed one dimension at a time, permitting control over the size of the computation and calling on well-established one-dimensional programs. Multidimensional processing offers a wider range of possible implementations as compared to one-dimensional processing, due to the greater flexibility of movement in the data indexing set. This increased freedom, along with large sized data sets typically found in multidimensional applications, places intensive demands on the communication aspects of the computation. Therefore, parallel programmers are facing greater challenges to develop efficient parallel FFT algorithms with minimum communication

overheads.

Because of its inherent algorithm structure, FFT lends itself naturally to parallel computation. There is a substantial amount of literature in parallelizing FFT, [28, 29, 30, 31, 32, 33, 34] to mention a few. In [28, 29, 30, 31] implementations of one-dimensional parallel FFTs on various multiprocessors were studied. In [32], implementation of high radix FFT on Boolean cube networks such as the Connection Machine was considered. Swarztrauber [34] investigated parallel FFT on general hypercube multiprocessors. He has derived an unordered parallel FFT algorithm on hypercube multiprocessors that has a minimum number of parallel data transfers between neighboring processors. This is performed by computing a one-dimensional FFT, which spans over processors. On the other hand, an existing two-dimensional FFT [35] in which FFTs on each dimension are computed by collecting all the required data and hence a computation is always within a node.

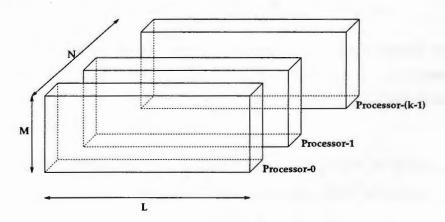

In Chapter 5, we presented an approach for computing multidimensional DFT on distributed memory systems that effectively utilizes the fact that today's distributed memory systems use wormhole routing for interprocessor communications. An approach to extend the algorithm for three or more dimensional problems using stride permutation and tensor product matrices has been presented that facilitates finding an efficient data-partitioning and network setup on distributed memory multiprocessors. Data-partitioning scheme is suitable and should be aimed at boundary value problems in fluid dynamics, finite element analysis etcetera. Results showed that our algorithm is more than six times as fast as the existing algorithm for certain cases. Moreover, higher the parallelism is, the better the performance of new algorithm will be. Given the fact that physical limits on memory exist at each processor, our new algorithm is a solution to today's large problems that involve multidimensional Fourier transform computations on massively parallel machines.

# 2.8 Survey of Matrix Algorithms

Many applications have numerical solutions in which computational burden is reduced partly or fully to matrix operations. One of the most elementary operations involving matrices is multiplication of two matrices. However, since matrix multiplication requires substantially more data movements than most other operations, algorithms that address efficient data movements are crucial to the effective implementation on concurrent computers.

For shared-memory systems, efficient parallel matrix computations are discussed in [36] with a theoretical package for parallel random access machines (PRAM). Without any optimization techniques, scalar operations in multiplication of two  $N \times N$  matrices is in order of  $O(N^3)$ . However, Strassen [37] discovered an algorithm that only uses  $O(N^{\log_2 7})$  scalar operations. Tensor product formulations of Strassen's algorithm are presented in [38, 39] along with capability to translate their mathematically equivalent tensor product formulations onto shared-memory architectures. Among algorithms constructed with an underlying topology in mind, Gentleman [40] has shown that for a mesh topology at least 0.35N routing steps are needed to compute product of two  $N \times N$  matrices while  $O(\log N)$  routes are necessary for a hypercube topology. For vector processors, Hayes [41] presented a technique at an element-by-element level for matrix-vector multiplication to solve systems of equations using iterative methods. She carried out implementation results on CYBER 205 demonstrating effectiveness for irregular problems.

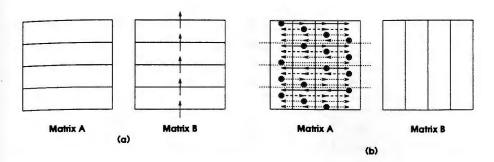

For distributed memory systems, communication between nodes is done through message passings. If two or more nodes try to access same data, the requests will be queued and each node will get the message in a different time slot. This fact is pronounced in [42]. However, it is assumed in [43, 44] that simultaneous memory requests by all processors can be served within the same time slot. In Chapter 6, we reviewed Fox et al's broadcast-and-shift matrix multiplication algorithm [25, 45] for message-passing architectures. This algorithm assumes mesh-division

data-partitioning for the underlying data. Multiplication algorithms in [42, 25, 45] require data movement of multiplicands irrespective of the size of the resulting matrix. Recently, Johnsson proposed an algorithm [46] to minimize the communication time in matrix multiplication. This algorithm is an evolution of considering two extreme cases of multiprocessor algorithm presented in [25, 45] but still requires data movement of multiplicands while results are accumulated in place.

Most existing research that has been reported in the literature for parallel matrix multiplications concentrates on mapping of the algorithm onto different topological structures. With the development of wormhole routing, algorithm performance becomes more sensitive to amount of data movements than the topological structures of the parallel machines being considered. Furthermore, all existing parallel matrix algorithms requires moving one or both multiplicands. In Chapter 6, we present an efficient algorithm [47] that requires no access of multiplicands by other processors due to the consideration of the unique data decomposition strategy. Only partial results need to be moved among processors. When compared to the algorithms in [25, 45, 46], messages in this algorithm are comparably shorter for the case of rectangular arrays. Performance improvements up to 440% have been observed over the algorithm in [25, 45] in actual implementations on Intel's Paragon and iPSC/860.

## 2.9 Experimental Environment

Intel's concurrent supercomputers are the cost-effective solution for large-scale applications. Experiments in this dissertation are performed on iPSC/860, Touchstone Delta, and Paragon supercomputers. All these systems consist of a set of processing nodes, I/O nodes, peripheral units, and a front-end processor. Each processing node uses one or more of the i860 multiprocessor. Message passing among nodes does not require any "store and forward" because of the Direct-Connect Module<sup>TM</sup> (DCM). With the DCM, one can view these systems as an ensemble of fully connected nodes with a uniform message latency. This means that programmers do not have to structure their application's communication according to the underlying

topology (physical connections between nodes). On each node, a node system software runs to provide message-passing capabilities, memory management, and process management.

The iPSC/860 uses hypercube topology for physical connection to link 64 nodes. Each node is a processor/memory pair with memory size 8M bytes. The runtime software on iPSC is NX operating system. The Touchstone Delta uses mesh topology for physical connection to link 512 nodes. Again, each node is a processor/memory pair with possible memory sizes 8M bytes and 16M bytes. The runtime software on Touchstone Delta is NX/1 operating system. The Paragon also uses mesh connectivity to connect 64 nodes. However, each node has two i860 processors one to perform computations and another to perform the necessary communication instructions. Hence, Paragon provides higher communication bandwidth than iPSC or Delta. Memory assignment for each can be 16M bytes or 32M bytes. Also, Paragon uses a more advanced runtime software called OSF/1 provided by Open Software Foundation.

The runtime environment consists of a set of user interface commands that can be issued at the UNIX prompt and a set of system calls that are available to host and node programs. The most common programming model used with these supercomputers is the "single program, multiple data" (SPMD) model. In this model, the same program runs on each node in the application, but each node works on only part of the data. Any requirements of the data for a node from another node is obtained using their corresponding runtime software. Due to the underlying assembly coded routing-scheme and uniform message latency characteristics, we assumed in our analysis that a message-passing between two nodes, irrespective of the nodes, will have same communication time.

# 2.10 Conclusion

Notation involved in a mathematical language to express, to segregate an application, and to allocate tasks on parallel systems is explained with relevant theorems. Survey of existing data-partition schemes, existing multiprocessor Fourier transform and matrix multiplication algorithms is presented. A brief description about the platforms on which experiments in this dissertation are conducted is presented.

# Chapter 3

# Data Partition and Migration: Formal Definitions

## 3.1 Storing Data in Distributed Memories

Most large scale applications of scientific computing involve manipulations of data that are expressed in terms of matrices and vectors. This is natural because matrix notation gives a compact way to express computation. Moreover, storing matrices or vectors in the memory of a computer system is the first step of any computation. Different ways of storing data may result in different algorithmic structures as well as different computational performance. While methodology and algebraic formulations for storing matrices in a linear memory space of a single processor system exist, such as row-major and column-major, there is neither a formal and commonly agreed way of addressing data stored in distributed memory multiprocessor systems, nor an agreed formal description for various storage schemes. Programmers for parallel machines usually organize data in a way based on their convenience and efficiency of a specific algorithm. As a result, data-allocation and -partition in parallel processing are very diversified. Therefore, there is a need for a unified approach for formalizing data-allocation and -partitioning in parallel machines, and for a clear and convenient mathematical representation of various data-storage schemes. In parallel computers, particularly in distributed memory multiprocessors, communication costs are directly related to various data-storage schemes. Clear representation of storage schemes

helps parallel programmer greatly to look into structures of implementations and communication costs associated with algorithms.

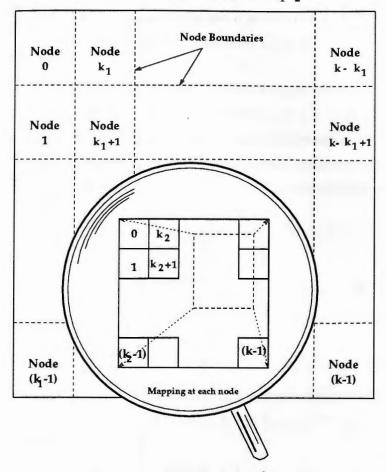

Consider a message-passing multiprocessor system with k processors labeled from 0 to k-1, where  $k=k_1$   $k_2$ . We would like to partition and store a two-dimensional (2D) matrix, denoted by  $\mathbf{A}$  onto this system. For the purpose of simplicity and clarity of our presentation, we present only the cases [27] where the data can be evenly divided into k subsets and concentrate on our main interest of algebraic representation of partitioning the matrix and storing them into processors' memories.

**Definition 3.1 Row-Division:** Let A be an  $M \times N$  matrix. We define row-division onto k processors as follows. Partition A into k sets of complete rows such that i-th set of rows (top-down) is allocated to i-th processor. In matrix notation, row-division can be represented as operating by

$$\mathbf{P}_{R}(M, N, k) = P(Nk, k) \otimes \mathbf{I}_{M/k}$$

(3.23)

on a vector  $\mathbf{a}$  that is formed as  $Vect_{MN}(\mathbf{A})$ .

We use bold faced "P" (P) with appropriate subscript to represent our datapartition definitions while italic "P" (P) to represent operation of stride permutation that explained in Section 2.3.

**Definition 3.2 Column-Division:** Let A be an  $M \times N$  matrix. We define column-division onto k processors as follows. Partitioning matrix A into k sets of complete columns such that i-th set of columns (left-right) is allocated to i-th processor. In matrix notation, column-division is represented as operating by

$$\mathbf{P}_C(M, N, k) = \mathbf{I}_{MN} \tag{3.24}$$

on a vector **a** that is formed as  $Vect_{MN}(\mathbf{A})$ .

**Definition 3.3 Mesh-Division:** Let A be an  $M \times N$  matrix. We define mesh-division of A onto a system with  $k_1 \times k_2$  processors as follows. Partition M rows

of A into  $k_1$  equal sets of rows (top-down) and then partition each set of rows into  $k_2$  equal subsets (left-right). Each subset is a  $M/k_1 \times N/k_2$  size matrix but will have neither complete rows nor complete columns. Allocation of these subsets to k processors is performed anti-lexicographically (top-down and then left-right). In matrix notation, mesh-division is defined as

$$\mathbf{P}_{M}(M, N, k_{1}, k_{2}) = \mathbf{I}_{k_{2}} \otimes P(Nk_{1}/k_{2}, k_{1}) \otimes \mathbf{I}_{M/k_{1}}.$$

(3.25)

Following three equations represent inverse operations of the above three definitions which can be derived using theorems 2.5 and 2.9.

$$\mathbf{P}_{R}^{-1}(M, N, k) = P(Nk, N) \otimes \mathbf{I}_{M/k}$$

(3.26)

$$\mathbf{P}_C^{-1}(M, N, k) = \mathbf{I}_{MN} \tag{3.27}$$

$$\mathbf{P}_{M}^{-1}(M, N, k_1, k_2) = \mathbf{I}_{k_2} \otimes P(Nk_1/k_2, N/k_2) \otimes \mathbf{I}_{M/k_1}$$

(3.28)

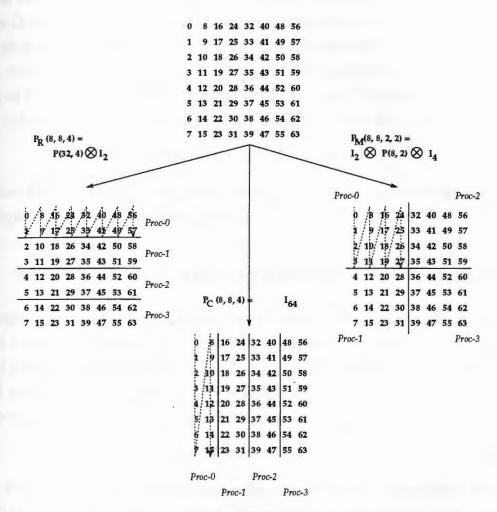

Example 3.1 This example demonstrates data partitioning of an  $8 \times 8$  matrix,  $\mathbf{A}$ , onto a 4-processor machine. Figure 3.1 shows how a 64-element vector  $\mathbf{a}$  formed by  $Vect_{64}(\mathbf{A})$  is partitioned in row-division, column-division, and mesh-division based on Definitions 3.1-3.3. In case of row-division,  $\mathbf{I}_2$  on the right-hand side of  $\mathbf{P}_R(8,8,4)$  represents moving vectors of length 2 according to the permutation matrix P(32,4). When this permutation is applied, resulting data at processor-0 is shown with dotted-line. For column-division data partitioning, since input permutation is an identity matrix, no action needs to be performed, and the vector  $\mathbf{a}$  is just segmented into four parts for allocating to four processors. For mesh-division data partitioning,  $\mathbf{I}_2$  on the left-hand side of  $\mathbf{P}_M(8,8,2,2)$  represents an action to divide the vector  $\mathbf{a}$  into two equal sets and perform the vector-stride action  $P(8,2) \otimes \mathbf{I}_4$  on each set. However, this vector-stride further divides each set into eight small subvectors of length 4 and shuffle them according to the permutation P(8,2). Once again, data residing at processor-0 after the action of input permutation is shown with dotted-line.

#### General Usage of Data-Partition Definitions

Consider any computational procedure that is expressed by an operational matrix

Figure 3.1: Action of data-partition algebraic expressions onto a 4-processor machine

G operating on a vector a to obtain vector b:

$$\mathbf{b} = \mathbf{G} \mathbf{a}. \tag{3.29}$$

This equation ignores the underlying data-partition necessary to carryout the computation in distributed memory multiprocessor system. To bring out the data-partition, let  $\hat{\mathbf{a}} (= \mathbf{Q}_1 \mathbf{a})$  be a desired data partition of  $\mathbf{a}$  among the processors where  $\mathbf{Q}_1$  is one of the data partition schemes  $(\mathbf{P}_R, \mathbf{P}_C, \text{ or } \mathbf{P}_M)$  defined above. If one expects the output data to be in a particular partition after the computation, then resultant data is of the form  $\hat{\mathbf{b}}$  where  $\hat{\mathbf{b}} = \mathbf{Q}_2 \mathbf{b}$  and  $\mathbf{Q}_2$  is also one of the definitions  $\mathbf{P}_R$ ,  $\mathbf{P}_C$ , or  $\mathbf{P}_M$  defined above. Then equation (3.29) can be rewritten as:

$$\hat{\mathbf{b}} = \mathbf{Q}_2 \ \mathbf{b} = \mathbf{Q}_2 \ \mathbf{G} \ \mathbf{a} = \begin{bmatrix} \mathbf{Q}_2 \ \mathbf{G} \ \mathbf{Q}_1^{-1} \end{bmatrix} \hat{\mathbf{a}} \stackrel{\text{def}}{=} \hat{\mathbf{G}} \hat{\mathbf{a}}$$

(3.30)

Therefore,  $\hat{\mathbf{G}} = \mathbf{Q}_2 \ \mathbf{G} \ \mathbf{Q}_1^{-1}$  is the actual-operational matrix that takes into account the complexity of considered data partition.

### 3.2 Moving Data Among Distributed Memories

Once input data is partitioned among the processors, data migrations at the interfaces between individual algorithms may be necessary in order to achieve global optimal performance of an application. One frequently used data migration in numerical applications is well known matrix transpose. Let  $\mathbf{a} = Vect_{MN}(\mathbf{A}_{M\times N})$ , and  $\mathbf{b} = Vect_{NM}(\mathbf{B}_{N\times M})$ , where  $\mathbf{B}_{N\times M}$  is the transpose of  $\mathbf{A}_{M\times N}$ . Then,

$$\mathbf{b} = P(MN, M) \mathbf{a}. \tag{3.31}$$

Hence P(MN, M) is the operational matrix for transpose algorithms, that is,  $\mathbf{G} = P(MN, M)$ . When data partition schemes are to be incorporated, the actual-operational matrix becomes  $\hat{\mathbf{G}}$  (see equation (3.30)). That is,

$$P(MN, M) = \mathbf{Q}_2^{-1} \; \hat{\mathbf{G}} \; \mathbf{Q}_1, \tag{3.32}$$

and the equation (3.31) becomes

$$\hat{\mathbf{b}} = \hat{\mathbf{G}} \, \hat{\mathbf{a}},\tag{3.33}$$

where  $\hat{\mathbf{G}} = \mathbf{Q}_2 P(MN, M) \mathbf{Q}_1^{-1}$ . In the following, we will show how to derive the operational matrices,  $\hat{\mathbf{G}}$ , required to transpose a matrix using the data-partitions defined in previous section (assume  $\mathbf{Q}_1 = \mathbf{Q}_2$  for simplicity) and discuss their implementation aspects via the tensor product formulations.

#### **ROW-DIVISION**

For row-division data partition, we have

$$\hat{\mathbf{G}} = \mathbf{P}_R(N, M, k) P(MN, M) \mathbf{P}_R^{-1}(M, N, k). \tag{3.34}$$

According to Definition 3.1, we have

$$\hat{\mathbf{G}} = \left[ P(Mk, k) \otimes \mathbf{I}_{N/k} \right] P(MN, M) \left[ P(Nk, N) \otimes \mathbf{I}_{M/k} \right], \tag{3.35}$$

(or)

$$\mathbf{G} = P(MN, M) = \left[ P(Mk, M) \otimes \mathbf{I}_{N/k} \right] \hat{\mathbf{G}} \left[ P(Nk, k) \otimes \mathbf{I}_{M/k} \right]. \tag{3.36}$$

Then, we can obtain expression for  $\hat{\mathbf{G}}$  by dissecting  $\mathbf{G} = P(MN, M)$  as:

$$P(MN, M) = [P(Mk, M) \otimes \mathbf{I}_{N/k}] [\mathbf{I}_k \otimes P(MN/k, M)]$$

by theorem 2.7

$$P(MN,M) = \mathbf{P}_{R}^{-1}(N,M,k) \left[ \mathbf{I}_{k^{2}} \otimes P(MN/k^{2},M/k) \right]$$

$$\left[ (\mathbf{I}_{k} \otimes P(N,k)) \otimes \mathbf{I}_{M/k} \right]$$

by theorem 2.8 and equation (3.26)

$$P(MN, M) = \mathbf{P}_{R}^{-1}(N, M, k) \left[ \mathbf{I}_{k} \otimes \mathbf{I}_{k} \otimes P(MN/k^{2}, M/k) \right]$$

$$\left[ P(k^{2}, k) \otimes \mathbf{I}_{N/k} \otimes \mathbf{I}_{M/k} \right] \left[ P(Nk, k) \otimes \mathbf{I}_{M/k} \right]$$

by applying theorem 2.7 to P(Nk, k)

$$P(MN, M) = \mathbf{P}_{R}^{-1}(N, M, k) \left[ \mathbf{I}_{k} \otimes \mathbf{I}_{k} \otimes P(MN/k^{2}, M/k) \right]$$

$$\left[ P(k^{2}, k) \otimes \mathbf{I}_{MN/k^{2}} \right] \mathbf{P}_{in}(\text{row}, M, N, k)$$

(3.37)

by Definition 3.1

$$P(MN, M) = \mathbf{P}_R^{-1} \hat{\mathbf{G}} \mathbf{P}_R.$$

me = my node number

for index = 1 to k - 1

myswap = xor(me,index)

Send block-myswap of my associated vector a to processor-myswap

Receive message from processor-myswap

Store message at block-myswap of my associated vector a

end

Table 3.2: Pseudo-code for message passing in transpose algorithms for either row-division or column-division partitions

Therefore, the actual-operational matrix in equation (3.33) for row-division partition can be expressed as two stages:

$$\hat{\mathbf{G}} = \left[ \mathbf{I}_k \otimes \mathbf{I}_k \otimes P(MN/k^2, M/k) \right] \left[ P(k^2, k) \otimes \mathbf{I}_{MN/k^2} \right]. \tag{3.38}$$

The first stage,  $P(k^2, k) \otimes \mathbf{I}_{MN/k^2}$ , is a global-task that involves message-passings among processors since the expression does not contain an identity matrix,  $\mathbf{I}_k$ , on left-hand side. The size of each message being passed is  $(MN/k^2)$  which is (1/k)th of the size of the data set residing at a processor. This is reflected in the above tensor product expression by  $\mathbf{I}_{MN/k^2}$ . The factor  $P(k^2, k)$  in the expression indicates that each processor has (k-1) subblocks to send out. Such message passings are carried out in (k-1) stages with one subblock being kept within a processor. The pseudo-code implementation for this stage is shown in Table 3.2.

The second stage,  $\underline{\mathbf{I}_k \otimes \mathbf{I}_k \otimes P(MN/k^2, M/k)}$ , represents a local-task due to the identity matrix  $\underline{\mathbf{I}_k}$  on the left-hand side. Each processor performs the parallel-stride operation  $[\underline{\mathbf{I}_k \otimes P(MN/k^2, M/k)}]$  locally.

#### **COLUMN-DIVISION**

For column-division data partition, we have

$$\hat{\mathbf{G}} = \mathbf{P}_C(N, M, k) P(MN, M) \mathbf{P}_C^{-1}(M, N, k)$$

(3.39)

According to Definition 3.2, we have

$$\hat{\mathbf{G}} = \mathbf{I}_{MN} P(MN, M) \mathbf{I}_{MN} = P(MN, M) = \mathbf{G}. \tag{3.40}$$

Then, we can obtain expression for  $\hat{\mathbf{G}}$  as:

$$P(MN, M) = [\mathbf{I}_k \otimes P(MN/k, M/k)] [P(Nk, k) \otimes \mathbf{I}_{M/k}]$$

by theorem 2.7

$$P(MN, M) = [\mathbf{I}_k \otimes P(MN/k, M/k)] [\{(P(k^2, k) \otimes \mathbf{I}_{N/k}) (\mathbf{I}_k \otimes P(N, k))\} \otimes \mathbf{I}_{M/k}]$$

by theorem 2.8

$$P(MN, M) = \left[\mathbf{I}_{k} \otimes P(MN/k, M/k)\right] \left[P(k^{2}, k) \otimes \mathbf{I}_{MN/k^{2}}\right]$$

$$\left[\mathbf{I}_{k} \otimes P(N, k) \otimes \mathbf{I}_{M/k}\right].$$

(3.41)

Therefore, the actual-operational matrix in equation (3.33) for column-division partitioning can be expressed as three stages:

$$\hat{\mathbf{G}} = \left[\mathbf{I}_k \otimes P(MN/k, M/k)\right] \left[P(k^2, k) \otimes \mathbf{I}_{MN/k^2}\right] \left[\mathbf{I}_k \otimes P(N, k) \otimes \mathbf{I}_{M/k}\right]$$

(3.42)

The first stage,  $\underline{\mathbf{I}_k \otimes P(N,k) \otimes \mathbf{I}_{M/k}}$ , represents local data permutations without message-passing due to the prior identity  $\underline{\mathbf{I}_k}$ . Each processor performs the vector-stride operation  $\left[P(N,k) \otimes \mathbf{I}_{M/k}\right]$  which moves N vectors with stride k, each vector is of length (M/k).

The second stage,  $\underline{P(k^2,k)} \otimes \underline{\mathbf{I}_{MN/k^2}}$ , is a global-task that is similar to message-passing stage explained in row-division transpose algorithm. Hence the total communication is again (k-1) messages, each message is of length  $(MN/k^2)$ .

The final stage,  $\underline{\mathbf{I}_k \otimes P(MN/k, M/k)}$ , is a and simple-stride permutation stage with stride (M/k) local to each processor. All processors carry out the same operation in parallel without communication.

#### **MESH-DIVISION**

For mesh-division partition, we have

$$\hat{\mathbf{G}} = \mathbf{P}_{M}(N, M, k_{2}, k_{1}) P(MN, M) \mathbf{P}_{M}^{-1}(M, N, k_{1}, k_{2}).$$

(3.43)

According to Definition 3.3, we have

$$\hat{\mathbf{G}} = \left[ \mathbf{I}_{k_1} \otimes P(Mk_2/k_1, k_2) \otimes \mathbf{I}_{N/k_2} \right] P(MN, M) \left[ \mathbf{I}_{k_2} \otimes P(Nk_1/k_2, N/k_2) \otimes \mathbf{I}_{M/k_1} \right],$$

(3.44)

(or)

$$P(MN, M) = \left[\mathbf{I}_{k_1} \otimes P(Mk_2/k_1, M/k_1) \otimes \mathbf{I}_{N/k_2}\right] \hat{\mathbf{G}} \left[\mathbf{I}_{k_2} \otimes P(Nk_1/k_2, k_1) \otimes \mathbf{I}_{M/k_1}\right].$$

(3.45)

Then we can obtain expression for  $\hat{\mathbf{G}}$  by decomposing  $\mathbf{G} = P(MN, M)$  as follows.

$$P(MN,M) = [\mathbf{I}_{k_1} \otimes P(MN/k_1, M/k_1)] [P(Nk_1, k_1) \otimes \mathbf{I}_{M/k_1}]$$

by theorem 2.7

$$P(MN,M) = \begin{bmatrix} \mathbf{I}_{k_1} \otimes P(Mk_2/k_1, M/k_1) \otimes \mathbf{I}_{N/k_2} \end{bmatrix} \begin{bmatrix} \mathbf{I}_k \otimes P(MN/k, M/k_1) \end{bmatrix}$$

$$[P(k,k_1) \otimes \mathbf{I}_{MN/k}] \begin{bmatrix} \mathbf{I}_{k_2} \otimes P(Nk_1/k_2, k_1) \otimes \mathbf{I}_{M/k_1} \end{bmatrix}$$

(3.46)

by theorem 2.8 on  $P(MN/k_1, M/k_1)$  and by theorem 2.7 on  $P(Nk_1, k_1)$

$$P(MN, M) = \mathbf{P}_{M}^{-1}(N, M, k_{2}, k_{1}) \left[ \mathbf{I}_{k} \otimes P(MN/k, M/k_{1}) \right]$$

$$\left[ P(k, k_{1}) \otimes \mathbf{I}_{MN/k} \right] \mathbf{P}_{M}(M, N, k_{1}, k_{2})$$

(3.47)

by equation (3.28) and Definition 3.3

$$P(MN, M) = \mathbf{P}_{M}^{-1}(N, M, k_{2}, k_{1}) \left[ P(k, k_{1}) \otimes \mathbf{I}_{MN/k} \right]$$

$$\left[ \mathbf{I}_{k} \otimes P(MN/k, M/k_{1}) \right] \mathbf{P}_{M}(M, N, k_{1}, k_{2})$$

(3.48)

by commutative law

$$P(MN, M) = \mathbf{P}_M^{-1} \hat{\mathbf{G}} \mathbf{P}_M$$

Therefore, the actual-operational matrix in equation (3.33) for mesh-division partition can be expressed as two stages in two different ways (equations (3.47) and (3.48)).

(a)

$$\hat{\mathbf{G}} = [\mathbf{I}_k \otimes P(MN/k), M/k_1)] [P(k, k_1) \otimes \mathbf{I}_{MN/k}],$$

and

(b)

$$\hat{\mathbf{G}} = [P(k, k_1) \otimes \mathbf{I}_{MN/k}] [\mathbf{I}_k \otimes P(MN/k, M/k_1)].$$

In case of (a), the first stage,  $P(k, k_1) \otimes \mathbf{I}_{MN/k}$ , is a global-task involving message-passings since there is no prior identity matrix. In fact, it is a single message-passing

| M    | N    | Row-Division | Col-Division | Mesh-Division |  |

|------|------|--------------|--------------|---------------|--|

|      |      | (msec)       | (msec)       | (msec)        |  |

| 128  | 128  | 5.236        | 6.172        | 1.316         |  |

| 128  | 256  | 5.902        | 7.051        | 2.028         |  |

| 128  | 512  | 9.031        | 10.409       | 2.159         |  |

| 128  | 1024 | 12.356       | 15.312       | 3.866         |  |

| 256  | 128  | 5.501        | 6.665        | 1.825         |  |

| 256  | 256  | 8.283        | 9.746        | 2.301         |  |

| 256  | 512  | 11.483       | 14.027       | 4.018         |  |

| 256  | 1024 | 20.076       | 22.503       | 7.548         |  |

| 512  | 128  | 8.310        | 9.432        | 3.450         |  |

| 512  | 256  | 11.555       | 13.359       | 5.905         |  |

| 512  | 512  | 18.536       | 21.122       | 7.954         |  |

| 512  | 1024 | 39.628       | 38.529       | 16.434        |  |

| 1024 | 128  | 11.228       | 13.132       | 5.815         |  |

| 1024 | 256  | 17.526       | 20.616       | 10.631        |  |

| 1024 | 512  | 31.211       | 37.445       | 20.889        |  |

| 1024 | 1024 | 50.936       | 66.403       | 49.274        |  |

Table 3.3: Experimental results of transpose algorithms on Intel's Paragon

routine with message size being (MN/k) as compared to (k-1) messages each of size  $(MN/k^2)$  in either row-division or column-division transpose algorithms.

The second stage,  $\underline{\mathbf{I}_k \otimes P(MN/k, M/k_1)}$ , represents that each processor executes a local simple-stride permutation because of prior identity matrix  $\underline{\mathbf{I}_k}$ . In fact, if we consider data at each processor to be a matrix of size  $M/k_1 \times N/k_2$ , then action to be performed in this stage is k local matrix transposes that are performed simultaneously on k processors.

# 3.2.1 Performance Evaluation of Three Transpose Algorithms

Transpose algorithms derived in Section 3.2 are implemented on Intel's Paragon and Touchstone Delta, and results are tabulated in Tables 3.3 and 3.4, respectively.

| M    | N    | Row-Division | Col-Division | Mesh-Division |  |

|------|------|--------------|--------------|---------------|--|

|      |      | (msec)       | (msec)       | (msec)        |  |

| 128  | 128  | 8.092        | 8.865        | 2.681         |  |

| 128  | 256  | 10.042       | 12.280       | 5.769         |  |

| 128  | 512  | 13.988       | 18.980       | 11.702        |  |

| 128  | 1024 | 23.909       | 33.014       | 20.018        |  |

| 256  | 128  | 10.065       | 12.016       | 5.041         |  |

| 256  | 256  | 14.228       | 18.150       | 11.554        |  |

| 256  | 512  | 23.030       | 31.237       | 20.088        |  |

| 256  | 1024 | 43.458       | 59.109       | 36.009        |  |

| 512  | 128  | 13.982       | 17.920       | 9.822         |  |

| 512  | 256  | 23.002       | 30.593       | 19.637        |  |

| 512  | 512  | 44.178       | 57.799       | 36.091        |  |

| 512  | 1024 | 95.145       | 114.215      | 79.681        |  |

| 1024 | 128  | 22.743       | 30.400       | 19.507        |  |

| 1024 | 256  | 42.197       | 57.171       | 36.109        |  |

| 1024 | 512  | 83.011       | 113.416      | 79.492        |  |

| 1024 | 1024 | 187.484      | 223.287      | 167.497       |  |

Table 3.4: Experimental results of transpose algorithms on Intel's Touchstone Delta

From the derivations in equations (3.38), (3.41), (3.47), and (3.48), we have seen that to transpose a matrix of size  $M \times N$  on a k-processor machine for row-division and column-division partitionings each requires (k-1) number of communications, each communication is of size  $(MN/k^2)$  while mesh-division partitioning requires one communication that is of size (MN/k). Though message length in mesh-division is k times more than that of any message in either row-division or column-division, results in Tables 3.3 and 3.4 clearly show that transpose algorithm for mesh-division eliminates the overheads to initiate a communication. These results also show that unlike uniprocessor algorithms, variations in data-decompositions can have a great impact on the performance of an algorithm.

# 3.3 An Example

As an example of applying our definition of data partitioning and migration, this section presents a typical two-dimensional (2D) fast Fourier transform (FFT) algorithm in a distributed memory system using our new formalism [48].

The summation form of the 2D-DFT on a matrix **X** of size  $M \times N$  is given by:

$$\mathbf{Y}(k,l) = \sum_{m=0}^{M-1} \left[ \sum_{n=0}^{N-1} \mathbf{X}(m,n) e^{-j\frac{2\pi nl}{N}} \right] e^{-j\frac{2\pi mk}{M}}$$

(3.49)

while tensor product representation of equation (3.49) can be written as:

$$\mathbf{y} = \underbrace{\left[\mathbf{F}_N \otimes \mathbf{F}_M\right]}_{\mathbf{G}} \mathbf{x},\tag{3.50}$$

where  $\mathbf{F}_J$  is a  $J \times J$  matrix with *i*th row, *j*th column entry equals to  $\exp(-j2\pi ik/J)$ ,  $j = \sqrt{-1}$ ,  $\mathbf{y} = Vect_{MN}(\mathbf{Y})$ ,  $\mathbf{x} = Vect_{MN}(\mathbf{X})$ , and  $\mathbf{G}$  is the operational matrix.

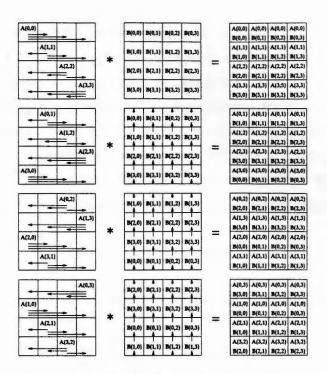

To compute the equation (3.50) on a k-processor parallel machine, we first parallelize the operational matrix by inserting identity matrices, assuming k divides both M and N. There are two ways of decomposing the equation (3.50): (a)  $\mathbf{y} = [\mathbf{I}_N \otimes \mathbf{F}_M][\mathbf{F}_N \otimes \mathbf{I}_M] \mathbf{x}$  which first computes Fourier transforms of columns followed by transforms of rows, and (b)  $\mathbf{y} = [\mathbf{F}_N \otimes \mathbf{I}_M][\mathbf{I}_N \otimes \mathbf{F}_M] \mathbf{x}$ , which performs transformation on rows followed by that on columns. Consider the first decomposition (a). The factor on the left-hand side represents a parallel computation of  $\mathbf{F}_M$  because of preceding identity matrix  $\mathbf{I}_N$  while the factor on the right-hand side cannot be done in parallel. To parallelize this stage of computation, we apply the commutative law presented in theorem 2.4, resulting in

$$\mathbf{y} = [\mathbf{I}_N \otimes \mathbf{F}_M] \ P(MN, N) \ [\mathbf{I}_M \otimes \mathbf{F}_N] \ P(MN, M) \ \mathbf{x}$$

(3.51)

If it is required that the Fourier transformed data be in the same data-partition scheme as the original data, then input data is  $\hat{\mathbf{x}} = \mathbf{P}_R \mathbf{x}$  and output data is  $\hat{\mathbf{y}} = \mathbf{P}_R \mathbf{y}$ . In such a case, equations (3.51) can be rewritten as:

$$\hat{\mathbf{y}} = \mathbf{P}_R \left[ \mathbf{I}_N \otimes \mathbf{F}_M \right] P(MN, N) \left[ \mathbf{I}_M \otimes \mathbf{F}_N \right] \left[ P(MN, M) \ \mathbf{P}_R^{-1} \right] \hat{\mathbf{x}}. \tag{3.52}$$

Note that if we used second parallelization (b), we would have obtained

$$\hat{\mathbf{y}} = [\mathbf{P}_R P(MN, N)] [\mathbf{I}_M \otimes \mathbf{F}_N] P(MN, M) [\mathbf{I}_N \otimes \mathbf{F}_M] \mathbf{P}_R^{-1} \hat{\mathbf{x}}. \tag{3.53}$$

In the following, we will see how we utilize our new definitions on data partition and migration to maximize the parallelism and minimize the communication cost while computing equation (3.52).

Consider row-division partitioning and start with the first stage operator (the right most factor) of equation (3.52). Recall that  $\mathbf{P}_R^{-1} = \left[P(Nk,N) \otimes \mathbf{I}_{M/k}\right]$  from Equation (3.23). It appears from equation (3.52) that neither  $\mathbf{P}_R^{-1} = \left[P(Nk,N) \otimes \mathbf{I}_{M/k}\right]$  nor P(MN,M) has a prior identity matrix  $\mathbf{I}_k$  implying that both operations involve message-passings. However, simple algebra manipulations of this computation stage based on our definitions can lead to a completely parallel computation. Decomposing  $P(MN,M)\mathbf{P}_R^{-1}$  in a different way, we have

$$P(MN, M)\mathbf{P}_{R}^{-1} = P(k(M/k)N, k(M/k))\mathbf{P}_{R}^{-1}$$

$$= [\mathbf{I}_{k} \otimes P(MN/k, M/k)] [P(Nk, k) \otimes \mathbf{I}_{M/k}] \mathbf{P}_{R}^{-1}$$

$$= [\mathbf{I}_{k} \otimes P(MN/k, M/k)]$$

$$\mathcal{Z}_{1}$$

(3.54)

No communication! For notational convenience, we use  $\mathcal{Z}_i$  to denote the *i*th computation stage. We will see shortly in this section that all the involved computation stages are directly computable using the existing subroutines in machine libraries of a commercial distributed memory multiprocessor.

The second stage of computation in equation (3.52) is obviously a parallel computation because of  $\mathbf{I}_{M}$ . The next stage, P(MN, N), can be factored as

$$P(MN, N) = \left[P(Nk, N) \otimes \mathbf{I}_{M/k}\right] \underbrace{\left[\mathbf{I}_{k} \otimes P(MN/k, N)\right]}_{\mathcal{Z}_{3}}$$

$$= \left[\left\{\left[\mathbf{I}_{k} \otimes P(N, N/k)\right] \left[P(k^{2}, k) \otimes \mathbf{I}_{N/k}\right]\right\} \otimes \mathbf{I}_{M/k}\right] \mathcal{Z}_{3}$$